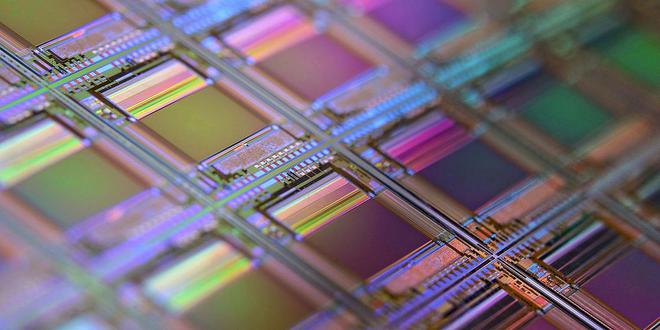

台积电2nm工艺进展:GAAFET技术加持下的性能与成本分析

台积电(TSMC)作为全球领先的半导体制造商,一直以来都在推动着先进制程技术的发展。近日,台积电宣布其2nm制程节点将首次采用环绕栅极晶体管(Gate-all-around FETs,简称GAAFET)技术,并且N2工艺还将支持NanoFlex技术,为芯片设计人员提供了更为灵活的标准元件。与现有的N3E工艺相比,N2工艺在性能和功耗方面均有显著提升,预计在相同功率下性能提升可达10%到15%,或者在相同频率下功耗降低25%到30%,同时晶体管密度也将提升15%。

成本分析:2nm晶圆价格飙升

根据相关报道,台积电每片300毫米直径的2nm晶圆的价格可能会超过3万美元,这一数字远高于先前预期的2.5万美元。相比之下,目前3nm晶圆的价格大约在1.85万至2万美元之间,而4/5nm晶圆的价格则在1.5到1.6万美元区间。由此可见,2nm晶圆的价格将有大幅度的提升。

投资与产能扩张

为了满足市场对2nm工艺技术的强大需求,台积电持续加大了对该制程节点的投资力度。2nm晶圆厂将分布在台湾北部的新竹宝山、中部的台中中科以及南部的高雄楠梓地区。新的工艺流程将增加极紫外光刻(EUV)步骤,甚至可能会采用双重曝光技术,这无疑将使得成本高于3nm制程节点。

生产计划与客户预期

台积电计划于2025年下半年开始N2工艺的批量生产,这意味着客户最早可以在2026年之前收到首批采用N2工艺制造的芯片。据推测,苹果公司将是N2工艺的首个客户,这也符合苹果一直以来追求尖端技术的传统。